# 4201A CLOCK GENERATOR

- Complete Clock Requirements for MCS-40<sup>™</sup> Systems

- Crystal Controlled Oscillator (XTAL External)

- MOS and TTL Level Clock Outputs

- Provides MCS-40 Reset Function Signal

- Standard Operating Temperature Range of 0° to 70° C

- Also Available with -40° to +85°C Operating Range

The 4201A is a CMOS integrated circuit designed to fill the clock requirements of the MCS-40 microcomputer family. The 4201A contains a crystal controlled oscillator (XTAL external), clock generation circuitry, and both MOS and TTL level clock driver circuits.

The 4201A also performs the power on reset function required by MCS-40 components and provides the logic necessary to implement the single-step function of the 4040 central processor unit.

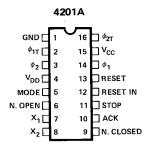

# PIN CONFIGURATION

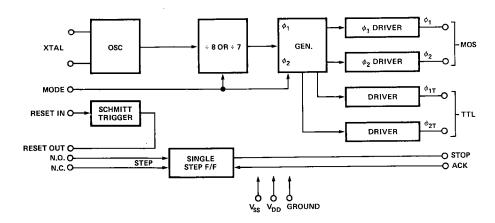

# **BLOCK DIAGRAM**

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

© Intel Corporation 1976

JULY 1976

# PIN DESCRIPTION

| Pin |             |                                                                                                                                  | Pin |             |                                                                                                                            |  |  |  |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------|-----|-------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| No. | Designation | Description of Function                                                                                                          | No. | Designation | Description of Function                                                                                                    |  |  |  |

| 1   | GND         | Circuit ground potential. This pin can be left floating for low power application. MOS clock output will be operative, TTL clock | 9   | N. CLOSED   | Input of single step circuitry to which normally closed contact of SPDT switch is connected.                               |  |  |  |

| 2   | $\phi$ IT   | outputs will not.  Phase 1 TTL level clock output. Positive true.                                                                | 10  | ACK         | Acknowledge input to single step circuitry normally connected to stop acknowledge output of 4040. The ACK input circuitry, |  |  |  |

| 3   | $\phi_2$    | Phase 2 MOS level clock output. Directly drives all MCS-40 components.                                                           |     |             | contains an internal pull-down resistor, eliminating the need for any external pull-down.                                  |  |  |  |

| 4   | $V_{DD}$    | Main Power Supply Pin. VDD = V <sub>CC</sub> -15V ±5%.                                                                           | 11  | STOP        | Stop output of single step circuitry normally connected to stop input of 4040. A SPDT                                      |  |  |  |

| 5   | MODE        | Counter mode control pin. Determines whether counter divides basic frequency by 8                                                |     |             | toggle switch may be inserted in this line for RUN/HALT control.                                                           |  |  |  |

|     |             | or 7. Mode 1 = V <sub>CC</sub> → ÷7                                                                                              | 12  | RESET IN    | Input to which RC network is connected to provide power-on reset timing.                                                   |  |  |  |

|     |             | Mode 2 = V <sub>DD</sub> → ÷8                                                                                                    | 13  | RESET       | Reset signal output which directly connects                                                                                |  |  |  |

| 6   | N. OPEN     | Input of single step circuitry to which normally open contact of SPDT switch is connected.                                       |     |             | to all MCS-40 reset inputs. This signal is active low.                                                                     |  |  |  |

| 7   | X1          | External Crystal Connection. This pin may be driven by an external frequency source. X2                                          | 14  | $\phi$ 1    | Phase 1 MOS level clock output. Directly drives all MCS-40 clock inputs.                                                   |  |  |  |

|     |             | should be left unconnected.                                                                                                      | 15  | vcc         | Circuit reference potential — most positive                                                                                |  |  |  |

| 8   | X2          | External Crystal Connection.                                                                                                     | 16  | фот         | supply voltage.  Phase 2 TTL level clock output. Positive                                                                  |  |  |  |

|     |             |                                                                                                                                  | .0  | <b>φ</b> 2Т | true.                                                                                                                      |  |  |  |

# **FUNCTIONAL DESCRIPTION**

The 4201A consists of the following functional blocks:

#### **CRYSTAL OSCILLATOR**

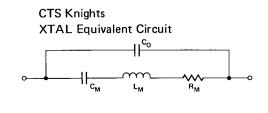

The oscillator circuit consists of a simple inverter biased in the active region and a crystal phase shift network to provide positive feedback.

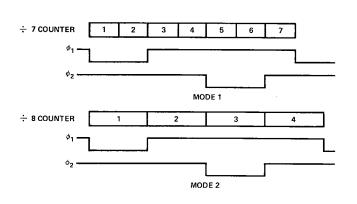

#### PROGRAMMABLE SHIFT REGISTER

The shift register in the 4201A divides the master clock and generates the proper states for generating the desired two-phase clock. The circuit is a seven bit dynamic device which circulates a logical "1" through a field of zeroes. The output of the various states are then combined to provide the proper clock waveforms. This provides a divide by 7 function.

In order to maintain the proper clock timing over the full operating frequency range of the MCS-40™ system, the shift

4201A Shift Register Modes.

register is programmable (using mode pin) as either a 7 bit or 8-bit device. In the 8-bit mode, the relationship between the phases is equal; that is,  $\phi_1$  pulse width,  $\phi_2$  pulse width,  $\phi_1$  to  $\phi_2$  and  $\phi_2$  to  $\phi_1$  times are all equal.

# **PHASE DECODER**

A simple gate complex is used to decode the shift register outputs to provide phase 1 and phase 2 clock waveforms. This circuitry is controlled by the mode input to achieve the two sets of timing discussed in the previous section.

#### **OUTPUT BUFFERS**

There are two sets of output buffers for the 2 phase clock. One set is the MOS level drivers designed to directly drive a full complement of MSC-40 components. The second set provides TTL compatible outputs which can drive one standard TTL load.

# RESET CIRCUIT

The reset circuit is simply a level detector and driver stage. An external RC network connected to the reset input pin of the 4201A as described in the Design Considerations section provides power-on delay. The user's system will determine the required delay.

# SINGLE STEP CONTROL

The 4201A contains the necessary circuitry for allowing the 4040 CPU to execute instructions one at a time. Using the stop input and stop acknowledge output of the 4040, the 4201A generates a pulse that allows the 4040 to perform only one instruction. The stop command can be provided by a SPDT pushbutton (break-before-make) directly since debouncing is provided by the 4201A. A SPST toggle switch, in series with the STOP line, provides the Run/Halt feature.

# **ABSOLUTE MAXIMUM RATINGS\***

| Storage Temperature                                     | -55°C to 150°C Ambient |

|---------------------------------------------------------|------------------------|

| Operating Temperature                                   | 0°C to 70°C Ambient    |

| Maximum Positive Voltage                                | V <sub>CC</sub> +.5V   |

| Maximum Negative Voltage                                | V <sub>DD</sub> 3V     |

| Maximum Power Dissipation                               | 1.0W                   |

| Maximum Supply Voltage V <sub>CC</sub> -V <sub>DD</sub> | ) 17V <sup>[1]</sup>   |

| Maximum Supply Voltage V <sub>CC</sub> -V <sub>DD</sub> | ) 17V <sup>[2]</sup>   |

Notes: 1. CLOAD,  $\phi_1$  and  $\phi_2 \ge 100$ pF.

# \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

# **D.C. CHARACTERISTICS** $T_A = 0^{\circ}C$ to $70^{\circ}C$ ; $V_{CC} - V_{DD} = 15V \pm 5\%$ ; $GND = V_{CC} - 5V \pm 5\%$ .

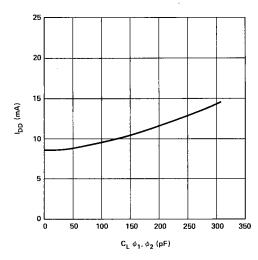

# **SUPPLY CURRENT**

|                 |                                                | Limit                |                       | Units | Conditions                                                                                               |  |

|-----------------|------------------------------------------------|----------------------|-----------------------|-------|----------------------------------------------------------------------------------------------------------|--|

| Symbol          | Parameter                                      | Min.                 | Max.                  | Units | Collations                                                                                               |  |

| I <sub>DD</sub> | Supply Current                                 |                      | 20                    | mA    | 5.185MHz Crystal, $C_{LOAD}$ $\phi_1$ and $\phi_2$ =200pF                                                |  |

| INPUT/OUT       | PUT CHARACTERISTICS                            |                      |                       |       |                                                                                                          |  |

| l <sub>Ll</sub> | Input Leakage Current                          |                      | 10                    | μΑ    | V <sub>IL</sub> = V <sub>DD</sub> All inputs except X <sub>1</sub> , X <sub>2</sub> , N. Open, N. Closed |  |

| V <sub>IH</sub> | Input High Voltage                             | V <sub>CC</sub> -1.5 | V <sub>CC</sub> +.5   | V     | All inputs except X <sub>1</sub> , X <sub>2</sub> , Reset                                                |  |

| V <sub>1L</sub> | Input Low Voltage                              | V <sub>DD</sub>      | V <sub>CC</sub> -13   | V     | All inputs except X <sub>1</sub> , X <sub>2</sub> , Reset                                                |  |

| VoL             | Output Low Voltage                             | $V_{DD}$             | V <sub>CC</sub> -13.4 | V     | Capacitance load only                                                                                    |  |

| V <sub>OH</sub> | Output High Voltage                            | V <sub>CC</sub> -1.5 | V <sub>CC</sub>       | V     | Capacitance load only                                                                                    |  |

| V <sub>OL</sub> | φ1Τ, φ2Τ                                       |                      | GND+.5                | V     | I <sub>OL</sub> = 1.6mA                                                                                  |  |

| V <sub>OH</sub> | φ <sub>1</sub> Τ, φ <sub>2</sub> Τ             | V <sub>CC</sub> 75   |                       | V     | I <sub>OH</sub> = -400μA                                                                                 |  |

| loL             | $\phi_1, \phi_2$ Sink Current                  | 400                  |                       | mA    | V <sub>OUT</sub> = V <sub>CC</sub> ; Pulse Width ≤1μsec                                                  |  |

| loL             | φ <sub>1T</sub> , φ <sub>2T</sub> Sink Current | 15                   |                       | mA    | V <sub>OUT</sub> = V <sub>CC</sub>                                                                       |  |

| loL             | Reset Sink Current                             | 6                    |                       | mA    | Vout = Vcc                                                                                               |  |

| loL             | Stop Sink Current                              | 1                    |                       | mA    | V <sub>OUT</sub> = V <sub>CC</sub>                                                                       |  |

| Іон             | $\phi_1, \phi_2$ Source Current                | 180                  |                       | mA    | V <sub>OUT</sub> = V <sub>DD</sub>                                                                       |  |

| Гон             | $\phi_{1T}$ , $\phi_{2T}$ Source Current       | 8                    |                       | mA    | V <sub>OUT</sub> = V <sub>DD</sub>                                                                       |  |

| Гон             | Reset Source Current                           | 6                    |                       | mA    | V <sub>OUT</sub> = V <sub>DD</sub>                                                                       |  |

| Іон             | Stop Source Current                            | 1                    |                       | mA    | V <sub>OUT</sub> = V <sub>DD</sub>                                                                       |  |

| VIL             | Reset Input Low Voltage                        | V <sub>DD</sub>      | V <sub>CC</sub> -11   | V     |                                                                                                          |  |

| V <sub>IH</sub> | Reset Input High Voltage                       | V <sub>CC</sub> -6.5 | V <sub>CC</sub> +.5   | V     |                                                                                                          |  |

| R <sub>1</sub>  | Pull Up Resistance on N. Open, N. Closed       | 20                   | 120                   | ΚΩ    | $V_{IN} = V_{DD}$                                                                                        |  |

# **CAPACITANCE** f = 1MHz; T<sub>A</sub> = 25°C

|                  | Parameter                                    | Limit |      | Units | Conditions                                        |  |

|------------------|----------------------------------------------|-------|------|-------|---------------------------------------------------|--|

| Symbol           |                                              | Min.  | Max. | Units | Conditions                                        |  |

| C <sub>IN</sub>  | Input Capacitance                            |       | 5    | pF    | All Inputs except X <sub>1</sub> , X <sub>2</sub> |  |

| C <sub>OUT</sub> | $\phi_1$ , $\phi_2$ Output Capacitance       |       | 40   | pF    |                                                   |  |

| C <sub>OUT</sub> | $\phi_{1T}$ , $\phi_{2T}$ Output Capacitance |       | 10   | pF    |                                                   |  |

| C <sub>OUT</sub> | Stop Reset Output Capacitance                |       | 5    | pF    |                                                   |  |

<sup>2.</sup> CLOAD,  $\phi_1$  and  $\phi_2$  = 0; R<sub>DD</sub> = 68 $\Omega$ ; Bypass Capacitor at V<sub>DD</sub> Pin to GND.

# **A.C. CHARACTERISTICS** $T_A = 0^{\circ}C$ to $70^{\circ}C$ ; $V_{CC} - V_{DD} = 15V \pm 5\%$ ; $G = V_{CC} - 5V \pm 5\%$

|                       |                                        | Limit                    |                      |                          |       | 0                                                                               |  |

|-----------------------|----------------------------------------|--------------------------|----------------------|--------------------------|-------|---------------------------------------------------------------------------------|--|

| Symbol                | Parameter                              | Min. Typ.                |                      | Max.                     | Units | Conditions                                                                      |  |

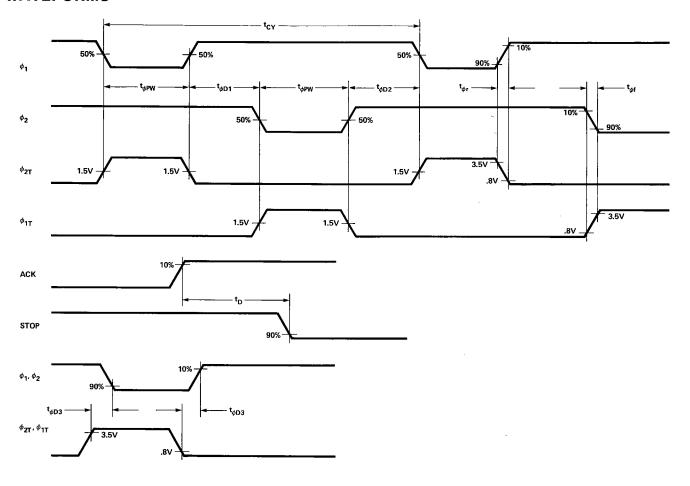

| tcY                   | Clock Period                           |                          | t <sub>XTAL</sub> *7 |                          | ns    |                                                                                 |  |

| t <sub>ø</sub> PW     | Clock Pulse Width                      | (2/7)t <sub>CY</sub> -10 | (2/7)t <sub>CY</sub> | (2/7)t <sub>CY</sub> +10 | ns    | Mode = V <sub>CC</sub>                                                          |  |

| t <sub>øD1</sub>      | Clock Delay from $\phi_1$ to $\phi_2$  | (2/7)t <sub>CY</sub> -10 | (2/7)t <sub>CY</sub> | (2/7)t <sub>CY</sub> +10 | ns    |                                                                                 |  |

| t <sub>øD2</sub>      | Clock Delay from $\phi_2$ to $\phi_1$  | (1/7)t <sub>CY</sub> -10 | (1/7)t <sub>CY</sub> | (1/7)t <sub>CY</sub> +10 | ns    |                                                                                 |  |

| tcY                   | Clock Period                           |                          | tXTAL *8             |                          | ns    |                                                                                 |  |

| t <sub>ø</sub> PW     | Clock Pulse Width                      | (1/4)t <sub>CY</sub> -10 | (1/4)t <sub>CY</sub> | (1/4)t <sub>CY</sub> +10 | ns    | Mada = V-                                                                       |  |

| t <sub>φ</sub> D1     | Clock Delay from $\phi_1$ to $\phi_2$  | (1/4)t <sub>CY</sub> -10 | (1/4)t <sub>CY</sub> | (1/4)t <sub>CY</sub> +10 | ns    | Mode = V <sub>DD</sub>                                                          |  |

| t <sub>øD2</sub>      | Clock Delay from $\phi_2$ to $\phi_1$  | (1/4)t <sub>CY</sub> -10 | (1/4)t <sub>CY</sub> | (1/4)t <sub>CY</sub> +10 | ns    | ]                                                                               |  |

| t <sub>øD3</sub>      | TTL Clk to MOS Clk Skew <sup>[1]</sup> | 0                        |                      | 40                       | ns    |                                                                                 |  |

| $t_{\phir},t_{\phif}$ | Clock Rise and Fall Time               |                          |                      | 50                       | ns    | $C_L$ =300pF= $\phi_1$ , $\phi_2$ ;<br>$C_L$ =50pF on $\phi_{1T}$ , $\phi_{2T}$ |  |

| t <sub>D</sub>        | Delay from Acknowledge to Stop         |                          |                      | 1                        | μs    | C <sub>L</sub> =20pF                                                            |  |

Note: 1. See waveforms section for phase relationships between  $\phi_1$ ,  $\phi_1 T$ ,  $\phi_2$ , and  $\phi_2 T$ .

# TYPICAL CHARACTERISTICS

# IDD CURRENT VS. LOAD CAPACITANCE

# **XTAL SPECIFICATIONS**

Range:

3.5 - 5.185 MHz

Mode:

Series or Parallel Resonant

Recommended: 1. Intel 14801

2. Crystek 5.185 MHz,

Spec. No. CY8A

3. CTS Knights MP051

XTAL Capacitance Requirements: 15-20 pF

≈ 3-5pF  $\approx$  10fF  $\leq$  50 $\Omega$  $R_{M}$  $(2\pi f)^2 C_M$

<sup>2.</sup> Proper system operation of all members of the MCS-401 component family is guaranteed with the 4201 Clock Generator at 1.35  $\mu$ sec  $\leq$ tCY  $\leq$  2  $\mu$ sec.

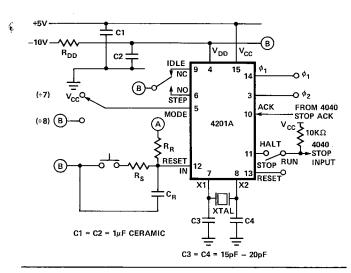

# **CLOCK GENERATOR IMPLEMENTATION**

# **DESIGN CONSIDERATIONS**

#### **CRYSTALS**

Either  $\div 7$  or  $\div 8$  Modes may be used. Mode equals  $V_{CC}$  for  $\div 7$ , Mode equals  $V_{DD}$  for  $\div 8$ . The clock frequency range should be between 500 kHz (4 MHz XTAL,  $\div 8$  MODE) and 740 kHz (5.185 MHz XTAL,  $\div 7$  MODE). The crystal may be found as a standard product from Intel distributors, CTS Knights or Crystek.

# X1 AND X2 INPUT CAPACITANCE

The XTAL terminals, X1 and X2, should be tied to 15 pF - 20 pF capacitors C3 and C4 to AC system GND.

# POWER SUPPLY VOLTAGE CONSIDERATIONS

1. Operation is guaranteed with  $V_{CC}-V_{DD}=15V\pm5\%$ . During system power-up or during power supply glitching, the maximum magnitude of  $(V_{CC}-V_{DD})$  must be limited to 17 volts.

During the power supply rise time (that is, when  $|V_{CC}-V_{DD}| < 14.25$  volts), improper  $\phi_1$ , and  $\phi_2$  output may occur until  $|V_{CC}-V_{DD}|$  reaches the 14.25 minimum voltage.

- 2. With  $V_{CC}$  = +5V,  $V_{DD}$  = -10V, bypass capacitor C1 of 1  $\mu$ F and C2 of 1  $\mu$ F from  $V_{CC}$  to GND and  $V_{DD}$  to GND, respectively, should provide excellent bypassing. Bypass capacitors should be ceramic or equivalent quality to insure low inductance and low series resistance.

- 3. The purpose of the current limiting register  $R_{DD}$  is both to limit  $\phi_1$  and  $\phi_2$  rise times and to drop  $V_{DD}$  at the 4201A  $V_{DD}$  pin. Values for  $R_{DD}$  as a function of  $\phi_1$ ,  $\phi_2$  load capacitance are:

For  $C_{LOAD}$  <50 pF; use  $R_{DD}$  = 100 $\Omega$ .

For 50 pF <C<sub>LOAD</sub> <100 pF; use R<sub>DD</sub> = 68 $\Omega$ .

For 100 pF <C<sub>LOAD</sub> <300 pF; use R<sub>DD</sub> = 27 $\Omega$ .

For  $C_{LOAD} > 300 \text{ pF}$ ; use  $R_{DD} = 10\Omega$ .

All 4201A functions requiring the  $V_{DD}$  voltage should use the pin  $V_{DD}$  or node B on the 4201A side of resistor  $R_{DD}$ . Operation with the voltage drop across  $R_{DD}$  is guaranteed by Intel testing.

4. Single-Supply System (+15 V or -15)

Recommended 4201A circuit modifications for single supply systems are:

- 1. The 1  $\mu$ F ceramic capacitor C1 should be between 4201A V<sub>DD</sub> and V<sub>CC</sub> pins.

- Other capacitors shown as being grounded should be connected to V<sub>CC</sub>.

- Reset R<sub>R</sub> is connected to V<sub>CC</sub>. Reset C<sub>R</sub> is connected to V<sub>DD</sub> pin.

- 4. The current limiting resistor  $R_{\mbox{\scriptsize DD}}$  is still needed in the  $V_{\mbox{\scriptsize DD}}$  line.

# 5. Power Supply Rise Times

Intel testing is for power supply rise times between 5 ms and 300 ms. For power supply rise times less than 5 ms, a 200K $\Omega$  resistor from X1 to GND and C3 = C4 = 5 pF is recommended.

# **RESET NETWORK**

The Reset input has  $V_{IL} = V_{CC}-11$  volts and  $V_{IH} = V_{CC}$ -6.5 volts, with about 1 volt of hysteresis (Schmitt circuit).

Node  $\bigcirc$  must be tied to GND or  $V_{CC}$  = +5 V; and  $R_R$  and  $C_R$  selected, such that the negative  $V_{DD}$  transition moves the Reset input below  $V_{IL}$ .

Tying node A to GND and making  $C_R$  very large, i.e.  $>1\mu\text{F}$ , will allow the greatest freedom in  $V_{CC}$  and  $V_{DD}$  rise times during turn-on. Tying node A to GND will also cause Reset after a  $V_{DD}$  glitch to GND.

The purpose of R<sub>S</sub> at 510 $\Omega$  or 1K $\Omega$  is to limit Reset input fall time on manual Reset, so that the Reset input does not fall below V<sub>DD</sub>.

# TTL CLOCK OUTPUTS

If  $\phi_{\rm IT}$  and  $\phi_{\rm 2T}$  are used, GND pin should be tied to logic ground.  $\phi_{\rm 2T}$  levels will swing between V<sub>CC</sub> and GND.

#### **UNUSED FUNCTIONS**

If any of the 4201A functions listed below are not used, for power conservation it is recommended that the pins be connected as described below:

1.  $\phi_{1T}, \phi_{2T}$

Tie GND pin,  $\phi_{1T}$ ,  $\phi_{2T}$  to  $V_{CC}$ .

2. Single step

Tie NO to  $V_{CC}$ . Tie NC to Node B ( $V_{DD}$  pin). Tie STOP ACK to  $V_{CC}$ . STOP left open.

3. Reset

Tie RESET IN, RESET OUT to VCC.

#### **WAVEFORMS**

# int<sub>e</sub>l°

Intel Corporation 3065 Bowers Avenue Santa Clara, California 95051 Tel: (408) 246-7501

TWX: 910-338-0026 TELEX: 34-6372

# U.S. AND CANADIAN SALES OFFICES

ALABAMA Glen White Associates 7844 Horseshoe Trail Huntsville 35802 Tel: (205) 883-9394

ARIZONA

Sales Engineering, Inc.

7155 E. Thomas Road, No. 6

Scottsdale 85252

Tel: (602) 994-3230

TWX: 910-950-1288

CALIFORNIA Intel Corp.\* 990 E. Arques Ave. Sulte 112 Sunnyvate 94086 Tel: (408) 738-3870 TWX: 910-338-9279 TWX: 910-338-0255

1WX: 910-338-025b Mac-I P.O. Box 1420 Cuperlino 95014 Tel: (408) 257-9880 Earle Associates, Inc. 4433 Convoy Street Sulle A San Diego 92111 Tel: (714) 278-5441 TWX: 910-335-1585 Intel Corp<sup>2</sup>. 1651 East 4th Street Sulle 28 Santa Ama 92701 Tel: (714) 385-9642 TWX: 910-995-1114

COLORADO Intel Corp. 12075 East 45th Avenue Suite 310 Denver 80239 Tel: (303) 373-4920 TWX: 810-932-0322

CONNECTICUT intel Corp. 8 Mill Plain Road Danbury 06810 Tel: (203) 792-8366 FLORIDA Intel Corp. 2020 W. McNab Road, Suite 104 Fl. Lauderdale 33309 Tel: (305) 971-7200 TWX: 510-955-9407 Intel Corp. 5151 Adanson Street, Suite 200-3 Orlando 3268-2393 TWX: 510-855-9219

ILLINOIS Intel Corp.\* 1000 Jorie Boulevard Suite 224 Oakbrook 60521 Tel: (312) 325-9510 TWX: 910-651-5881

IOWA Technical Representatives, Inc. 1703 Hillside Drive Cedar Rapids Tel: (319) 396-5662

KANSAS Technical Representatives, Inc. 801 Clairborne Olathe 66081 Tel (913) 782-1177 TWX: 910-749-6412

MARYLAND Glen White Associates 57 West Timonium Road Timonium 21093 Tel: (301) 252-7742

let: (301) 252-7742 Intel Corp.\*\* 57 West Timonlum Road Sulte 307 Timonlum 21093 Tel: (301) 252-7742 TWX: 710-232-1807

MASSACHUSETTS Intel Corp.\* 187 Billerica Road, Suite 14A Chelmsford 01824 Tel: (617) 861-1136 TWX: 710-343-6333 MICHIGAN Intel Corp. 725 South Adams Road Suite 288 Birmingham 48011 Tel: (313) 642-7018 TWX: 910-420-1212 TELEX: 2 31143

MINNESOTA Intel Corp. 675 Southgate Office Plaza 5001 West 80th Street Bloomington 55437 Tel: (612) 835-6722 TWX: 910-576-2867

MISSOURI

Technical Representatives, Inc.

Trade Center Bidg.

300 Brookes Drive, Suite 108

Hazelwood 63042

Tel: (314) 731-5200

TWX: 910-762-0618

NEW JERSEY Intel Corp. 2 Kilmer Road Edison 08617 Tel: (201) 985-9100 TWX: 710-480-8238

NEW YORK Intel Corp.\* 6901 Jeriche Turnpike Syosset 11791 Tel: (516) 864-9860 TWX: 510-221-2199 Intel Corp. 474 Thurston Road Rochester, N.Y. 14619 Tel: (716) 328-7340 TWX: 510-253-3841 NEW YORK (cont.) T-Squared 3522 James Street Syracuse 13206 Tel: (315) 463-8592 TWX: 710 541-0554

Tei: (315) 463-6592 TWX: 710 541-0554 T-Squared 640 Cralg Road P.O. Box W Pittstord 14534 Tei: (716) 381-2551 TELEX: 97-8289 Intel Corp. 55 Market Street Poughkeepsle, New York 12601 Tei: (914) 473-2303

NORTH CAROLINA Glen White Associates 913 Plateau Lane Raleigh 27609 Tel: (919) 876-5617

OHIO

Intel Corp. \*

8312 North Main Street

Dayton 45415

Tel: (513) 899-5350

TELEX: 288-004

Intel Corp. \*

26250 Euclid Ave.

Suite 531F

Euclid 44132

Tel: (216) 289-0101

PENNSYLVANIA Intel Corp.\* 520 Pennsylvania Ave. Fort Washington 19034 Tel: (215) 542-9444 TWX: 510-661-0709 TENNESSEE Glen White Associates 206 Chickasaw Drive Johnson City 37601 Tel: (615) 928-0184

TEXAS

Evans & McDowell Associat

13777 N. Central Expresswa

Sulte 405

Dallas 75231

Tel: (214) 238-7-157

TWX: 910-867-4763

Evans & McDowell Associat

6510 Harwin. Avenue, Suite

Houston 77036

Tel: (713) 793-2900

Intel Corp.\*

6350 L.B.J. Freeway

Suite 178

Dallas 75240

Tel: (214) 661-8829

TWX: 910-860-5467

VIRGINIA Glen White Associates P.O. Box 1104 Lynchburg 24505 Tel: (804) 846-4624

WASHINGTON E.S./Chase Co. P.O. Box 80903 Seattle 98108 Tel: (206) 762-4824 Twx: 910-444-2298

CANADA Intel Corp. 70 Chamberlain Ave. 70 Chamberlain Ave. Ottawa, Ontario K15 1V9 Tel: (613) 232-6576 TELEX: 053-4419 Multillek, Inc. 4 Barren Street Ottawa, Ontario K2J 1G2 Tel: (613) 825-4695 TELEX: 053-4685