# iSBC® 188/56 ADVANCED COMMUNICATING COMPUTER

- iSBC<sup>®</sup> Single Board Computer or Intelligent Slave Communication Board

- 8 Serial Communications Channels, Expandable to 12 Channels on a Single MULTIBUS<sup>®</sup> Board

- 8 MHz 80188 Microprocessor

int

- Supports RS232C Interface on 6 Channels, RS422A/449 or RS232C Interface Configurable on 2 Channels

- Supports Async, Bisync HDLC/SDLC, On-Chip Baud Rate Generation, Half/ Full-Duplex, NRZ, NRZI or FM Encoding/Decoding

- 7 On-Board DMA Channels for Serial I/O, 2 80188 DMA Channels for the iSBX™ MULTIMODULE™ Board

- MULTIBUS Interface for System Expansion and Multimaster Configuration

- Two iSBX Connectors for Low Cost I/O Expansion

- 256K Bytes Dual-Ported RAM On-Board

- Two 28-pin JEDEC PROM Sites Expandable to 6 Sites with the iSBC 341 MULTIMODULE Board for a Maximum of 192K Bytes EPROM

- Resident Firmware to Handle up to 12 RS232C Async Lines

The iSBC 188/56 Advanced Communicating Computer (COMMputer™) is an intelligent 8-channel single board computer. This iSBC board adds the 8 MHz 80188 microprocessor-based communications flexibility to the Intel line of OEM microcomputer systems. Acting as a stand-alone CPU or intelligent slave for communication expansion, this board provides a high performance, low-cost solution for multi-user systems. The features of the iSBC 188/56 board are uniquely suited to manage higher-layer protocol requirements needed in today's data communications applications. This single board computer takes full advantage of Intel's VLSI technology to provide state-of-the-art, economic, computer based solutions for OEM communications-oriented applications.

280715-1

\*IBM is a registered trademark of International Business Machines \*UNIX is a trademark of Bell Laboratories \*XENIX is a trademark of Microsoft Corporation

# **OPERATING ENVIRONMENT**

The iSBC 188/56 COMMputer™ features have been designed to meet the needs of numerous communications applications. Typical applications include:

- 1. Terminal/cluster controller

- 2. Front-end processor

- 3. Stand-alone communicating computer

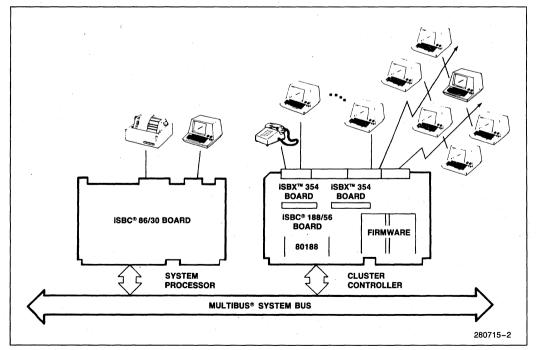

## **Terminal/Cluster Controller**

A terminal/cluster controller concentrates communications in a central area of a system. Efficient handling of messages coming in or going out of the system requires sufficient buffer space to store messages and high speed I/O channels to transmit messages. More sophisticated applications, such as cluster controllers, also require character and format conversion capabilities to allow different types of terminals to be attached.

The iSBC 188/56 Advanced Communicating Computer is well suited for multi-terminal systems (see Figure 1). Up to 12 serial channels can be serviced in multi-user or cluster applications by adding two iSBX 354 MULTIMODULE boards. The dual-port RAM provides a large on-board buffer to handle incoming and outgoing messages at data rates up to 19.2K baud. Two channels are supported for continuous data rates greater than 19.2K baud. Each serial channel can be individually programmed for different baud rates to allow system configurations with differing terminal types. The firmware supplied on the iSBC 188/56 board supports up to 12 asynchronous RS232C serial channels, provides modem control and performs power-up diagnostics. The high performance of the on-board CPU provides intelligence to handle protocols and character handling typically assigned to the system CPU. The distribution of intelligence results in optimizing system performance by releasing the system CPU of routine tasks.

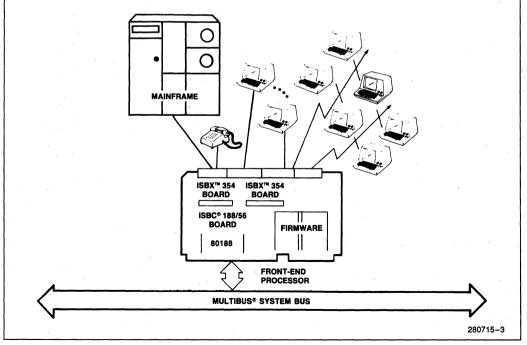

### **Front-End Processor**

A front-end processor off-loads a system's central processor of tasks such as data manipulation and text editing of characters collected from the attached terminals. A variety of terminals require flexible terminal interfaces. Program code is often dynamically downloaded to the front-end processor from the system CPU. Downloading code requires sufficient memory space for protocol handling and program code. Flow control and efficient handling of interrupts require an efficient operating system to manage the hardware and software resources.

#### Figure 1. Terminal/Cluster Controller Application

The iSBC 188/56 board features are designed to provide a high performance solution for front-end processor applications (see Figure 2). A large amount of random access memory is provided for dynamic storage of program code. In addition, local memory sites are available for storing routine programs such as X.25, SNA or bisync protocol software. The serial channels can be configured for links to mainframe systems, point-to-point terminals, modems or multidrop configurations.

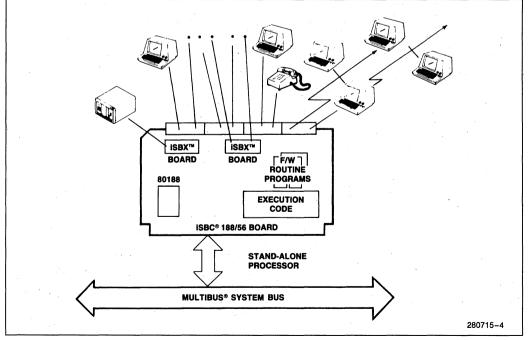

## Stand-Alone COMMputer™ Application

A stand-alone communication computer is a complete computer system. The CPU is capable of managing the resources required to meet the needs of multi-terminal, multi-protocol applications. These applications typically require multi-terminal support, floppy disk control, local memory allocation, and program execution and storage.

To support stand-alone applications, the iSBC 188/56 COMMputer board uses the computational capabilities of an on-board CPU to provide a high-speed system solution controlling 8 to 12 channels of serial I/O (see Figure 3). The local memory available is large enough to handle special purpose code, execution code and routine protocol software.

The MULTIBUS interface can be used to access additional system functions. Floppy disk control and graphics capability can be added to the iSBC standalone computer through the iSBX connectors.

## ARCHITECTURE

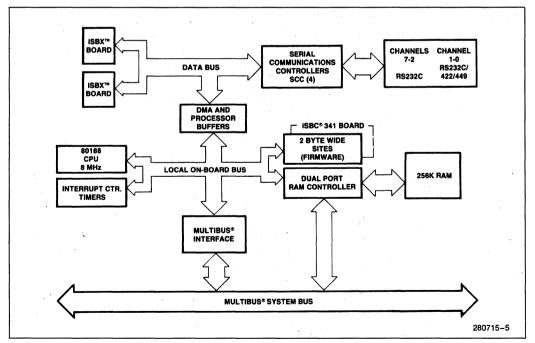

The four major functional areas are Serial I/O, CPU, Memory and DMA. These areas are illustrated in Figure 4.

## Serial I/O

Eight HDLC/SDLC serial interfaces are provided on the iSBC 188/56 board. The serial interface can be expanded to 12 channels by adding 2 iSBX 354 MULTIMODULE boards. The HDLC/SDLC interface is compatible with IBM\* system and terminal equipment and with CCITT's X.25 packet switching interface.

Four 82530 Serial Communications Controllers (SCC) provide eight channels of half/full duplex serial I/O. Six channels support RS232C interfaces. Two channels are RS232C/422/449 configurable and can be tri-stated to allow multidrop networks. The 82530 component is designed to satisfy several serial communications requirements; asynchronous,

#### Figure 2. Front-End Processor Application

byte-oriented synchronous (HDLC/SDLC) modes. The increased capability at the serial controller point results in off-loading the CPU of tasks formerly assigned to the CPU or its associated hardware. Configurability of the 82530 allows the user to configure it to handle all asynchronous data formats regardless of data size, number of start or stop bits, or parity requirements. An on-chip baud rate generator allows independent baud rates on each channel.

The clock can be generated either internally with the SCC chip, with an external clock or via the NRZ1 clock encoding mechanism.

All eight channels can be configured as Data Terminal Equipment (DTE) or Data Communications Equipment (DCE). Table 1 lists the interfaces supported.

| Connection     | Synchronous     | Asynchronous<br>Modem to Direct |  |

|----------------|-----------------|---------------------------------|--|

| Connection     | Modem to Direct |                                 |  |

| Point-to-Point | X**             | X                               |  |

|                | Channels        | Channels                        |  |

| Multidrop      | 0 and 1         | 0 and 1                         |  |

| Loop           | х               | N/A                             |  |

\*\*All 8 channels are denoted by X.

# Central CPU

The 80188 central processor component provides high performance, flexibility and powerful processing. The 80188 component is a highly integrated microprocessor with an 8-bit data bus interface and a 16-bit internal architecture to give high performance. The 80188 is upward compatible with 86 and 186 software.

The 80188/82530 combination with on-board PROM/EPROM sites, and dual-port RAM provide the intelligence and speed to manage multi-user, multi-protocol communication operations.

#### Memory

There are two areas of memory on-board: dual-port RAM and universal site memory. The iSBC 188/56 board contains 256K bytes of dual-port RAM that is addressable by the 80188 on-board. The dual-port memory is configurable anywhere in a 16M byte address space on 64K byte boundaries as addressed from the MULTIBUS port. Not all of the 256K bytes are visible from the MULTIBUS bus side. The amount of dual-port memory visible to the

Figure 3. Stand-Alone COMMputer™ Application

MULTIBUS side can be set (with jumpers) to none, 16K bytes, or 48K bytes. In a multiprocessor system these features provide local memory for each processor and shared system memory configurations where the total system memory size can exceed one megabyte without addressing conflicts.

The second area of memory is universal site memory providing flexible memory expansion. Two 28-pin JEDEC sockets are provided. One of these sockets is used for the resident firmware as described in the FIRMWARE section.

The default configuration of the boards supports 16K byte EPROM devices such as the Intel 27128 component. However, these sockets can contain ROM, EPROM, Static RAM, or EEPROM. Both sockets must contain the same type of component (i.e. as the first socket contains an EPROM for the resident firmware, the second must also contain an EPROM with the same pinout). Up to 32K bytes can be addressed per socket giving a maximum universal site memory size of 64K bytes. By using the iSBC 341 MULTIMODULE board, a maximum of 192K bytes of universal site memory is available. This provides sufficient memory space for on-board network or resource management software.

## **On-Board DMA**

Seven channels of Direct Memory Access (DMA) are provided between serial I/O and on-board dual port RAM by two 8237-5 components. Each of channels 0, 1, 2, 3, 5, 6, and 7 is supported by their own DMA line. Serial channels 0 and 1 are configurable for full duplex DMA. Configuring the full duplex DMA option for Channels 0 and 1 would require Channels 2 and 3 to be interrupt driven or polled. Channel 4 is interrupt driven or polled only.

Two DMA channels are integrated in the 80188 processor. These additional channels can be connected to the iSBX interfaces to provide DMA capability to iSBX MULTIMODULE boards such as the iSBX 218A Floppy Disk Controller MULTIMODULE board.

## **OPERATING SYSTEM SUPPORT**

Intel offers run-time foundation software to support applications that range from general purpose to high-performance solutions.

Figure 4. Block Diagram of iSBC® 188/56 Board

Release 6 of the iRMX 86 Operating System provides a rich set of features and options to support sophisticated stand-alone communications applications on the iSBC 188/56 Advanced Communicating Computer. In addition to supporting real-time requirements, the iRMX 86 Operating System Release 6 has a powerful, yet easy to use human interface. Services provided by the iRMX 86 Operating System include facilities for executing programs concurrently, sharing resources and information, servicing asynchronous events and interactively controlling system resources and utilities. The iRMX 86 Operating System is readily extended to support assembler, PL/M, PASCAL, and FORTRAN software development environments. The modular building block software lends itself well to customized application solutions. If the iSBC 188/56 board is acting as an intelligent slave in a system environment, an iRMX 86 driver resident in the host CPU can be written by following the examples in the manual "Guide to Writing Device Driven for iRMX 86 and iRMX 88 I/O Systems".

The iSDM™ 86 System Debug Monitor supports target system debugging for the iSBC 188/56 Advanced Communicating COMMputer board. The monitor contains the necessary hardware, software and documentation required to interface the iSBC 188/56 target system to an Intel microcomputer development system for debugging application software.

The XENIX\* 286 Operating System, Release 3, is a fully licensed adaptation of the Bell Laboratories System III UNIX\* Operating System. The XENIX system is an interactive, protected, multi-user, multitasking operating system with a powerful, flexible human interface. Release 3 of XENIX 286 includes a software driver for the iSBC 188/56 board (and up to two iSBX 354 MULTIMODULE Boards) acting as an intelligent slave for multi-user applications requiring multiple persons running independent, terminal-oriented jobs. Example applications include distributed data processing, business data processing, software development and engineering or scientific data analvsis. XENIX 286 Release 3 Operating System services include device independent I/O, tree-structured file directory and task hierarchies, re-entrant/shared code and system accounting and security access protection.

| Feature                                | Description                                                                                                                                                                                                       |  |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Asynchronous Serial<br>Channel Support | Supports the serial channels in asynchronous ASCII mode.<br>Parameters such as baud rate, parity generation, parity<br>checking and character length can be programmed<br>independently for each channel.         |  |

| Block Data Transfer<br>(On Output)     | Relieves the host CPU of character-at-a-time interrupt<br>processing. The iSBC 188/56 board accepts blocks of data for<br>transmission and interrupts the processor only when the entire<br>block is transmitted. |  |

| Limited Modem Control                  | Provides software control of the Data Terminal Ready (DTR)<br>line on all channels. Transitions on the Carrier Detect (CD) line<br>are sensed and reported to the host CPU.                                       |  |

| Tandem Modem Support                   | Transmits an XOFF character when the number of characters<br>in its receive buffer exceeds a threshold value and transmits an<br>XON character when the buffer drains below some other<br>threshold.              |  |

| Download and<br>Execute Capability     | Provides a capability for the host CPU to load code anywhere in the address space of the iSBC 188/56 board and to start executing at any address in its address space.                                            |  |

| Power Up<br>Confidence Tests           | On board reset, the firmware executes a series of simple tests to establish that crucial components on the board are functional.                                                                                  |  |

Table 2. Features of the iSBC® 188/56 Firmware

#### FIRMWARE

The iSBC 188/56 Communicating COMMputer board is supplied with resident firmware that supports up to 12 RS232C asynchronous serial channels. In addition, the firmware provides a facility for a host CPU to download and execute code on the iSBC 188/56 board. Simple power-up confidence tests are also included to provide a quick diagnostic service. The firmware converts the iSBC 188/56 COMMputer board to a slave communications controller. As a slave communications controller, it requires a separate MULTIBUS host CPU board and requires the use of MULTIBUS interrupt line to signal the host processor. Table 2 summarizes the features of the firmware. nent. The two controllers are configured with the 80130 controller as the master and the 80188 controller as the slave. Two of the 80130 interrupt inputs are connected to the 82530 serial controller components to provide vector interrupt capabilities by the serial controllers. The iSBC 188/56 board provides 22 interrupt levels. The highest level is the NMI (Non-Maskable Interrupt) line which is directly tied to the 80188 CPU. This interrupt is typically used for signaling catastrophic events (e.g. power failure). There are 5 levels of interrupts internal to the 80188 processor. Another 8 levels of interrupts are available from the 80130 component. Of these 8, one is tied to the programmable interrupt controller (PIC) of the 80188 CPU. An additional 8 levels of interrupts are available at the MULTIBUS interface. The iSBC 188/56 board does not support bus vectored interrupts. Table 3 lists the possible interrupt sources.

80188 processor and the other in the 80130 compo-

## INTERRUPT CAPABILITY

The iSBC 188/56 board has two programmable interrupt controllers (PICs). One is integrated into the

| Device                              | Function                                                                                                                                      | Number of<br>Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MULTIBUS Interface<br>INT0-INT7     | Requests from MULTIBUS resident peripherals or other CPU boards.                                                                              | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 82530 Serial Controllers            | Transmit buffer empty, receive buffer full and channel errors 1 and external status.                                                          | 8 per 82530<br>Total = 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Internal 80188<br>Timer and DMA     | Timer 0, 1, 2 outputs and 2 DMA channel interrupts.                                                                                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 80130 Timer Outputs                 | Timer 0, 1, 2 outputs of 80130.                                                                                                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Interrupt from Flag<br>Byte Logic   | Flag byte interrupt set by MULTIBUS master (through MULTIBUS® I/O Write).                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Bus Flag Interrupt                  | Interrupt to MULTIBUS® (Selectable for INT0 to INT7) generated from on-board 80188 I/O Write.                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| iSBX Connectors<br>iSBX DMA         | Function determined by iSBX MULTIMODULE board.<br>DMA interrupt from iSBX (TDMA).                                                             | 4 (Two per<br>Connector)<br>2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Bus Fail-Safe Timeout<br>Interrupt. | Indicates iSBC 188/48 board timed out either waiting for<br>MULTIBUS access or timed out from no acknowledge<br>while on MULTIBUS System Bus. | 1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Latched Interrupt                   | Converts pulsed event to a level interrupt. Example: 8237A-5 EOP.                                                                             | territoria de la composición de la compos |

| OR-Gate Matrix                      | Concentrates up to 4 interrupts to 1 interrupt (selectable by stake pins).                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Ring Indicator<br>Interrupt         | Latches a ring indicator event from serial channels 4, 5, 6, or 7.                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| NOR-Gate<br>Matrix                  | Inverts up to 2 interrupts into 1 (selectable by stake pins).                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Table 3. Interrupt Request Sources

## SUPPORT FOR THE 80130 COMPONENT

Intel does not support the direct processor execution of the iRMX nucleus primitives from the 80130 component. The 80130 component provides timers and interrupt controllers.

## **EXPANSION**

### **EPROM Expansion**

Memory may be expanded by adding Intel compatible memory expansion boards. The universal site memory can be expanded to six sockets by adding the iSBC 341 MULTIMODULE board for a maximum total of 192K bytes of universal site memory.

#### ISBX™ MULTIMODULE™ Expansion Module

Two 8-bit iSBX MULTIMODULE connectors are provided on the iSBC 188/56 board. Using iSBX modules additional functions can be added to extend the I/O capability of the board. In addition to specialized or custom designed iSBX boards, there is a broad range of iSBX MULTIMODULE boards from the Intel including parallel I/O, analog I/O, IEEE 488 GPIB, floppy disk, magnetic bubbles, video and serial I/O boards.

The serial I/O MULTIMODULE boards available include the iSBX 354 Dual Channel Expansion MULTI-MODULE board. Each iSBX 354 MULTIMODULE board adds two channels of serial I/O to the iSBC 188/56 board for a maximum of twelve serial channels. The 82530 serial communications controller on the MULTIMODULE board handles a large variety of serial communications protocols. This is the same serial controller as is used on the iSBC 188/56 board to offer directly compatible expansion capability for the iSBC 188/56 COMMputer board.

## **MULTIBUS® INTERFACE**

The iSBC 188/56 Advanced COMMputer board can be a MULTIBUS master or intelligent slave in a multimaster system. The iSBC 188/56 board incorporates a flag byte signalling mechanism for use in multiprocessor environments where the iSBC 188/56 board is acting as an intelligent slave. The mechanism provides an interrupt handshake from the MULTIBUS System Bus to the on-board-processor and vice-versa. The Multimaster capabilities of the iSBC 188/56 board offers easy expansion of processing capacity and the benefits of multiprocessing. Memory and I/O capacity may be expanded and additional functions added using Intel MULTIBUS compatible expansion boards.

## SPECIFICATIONS

# Word Size

Instruction—8, 16, 24 or 32 bits Data Path—8 bits Processor Clock 82530 Clock DMA Clock 8 MHz 4.9152 MHz 4 MHz

#### Dual Port RAM

iSBC 188/56 Board-256 bytes

As viewed from the 80188-64K bytes

As viewed from the MULTIBUS System Bus-Choice: 0, 16K or 48K

#### EPROM

| iSBC® 188/56<br>Board Using: | Size | On Board<br>Capacity | Address Range            |

|------------------------------|------|----------------------|--------------------------|

| 2732                         | 4K   | 8K bytes             | FE000-FFFFFH             |

| 2764                         | 8K   | 16K bytes            | FC000-FFFFFH             |

| 27128                        | 16K  | 32K bytes            | F8000-FFFFFH             |

| 27256                        | 32K  | 64K bytes            | F0000-FFFFFH             |

| 27512                        | 64K  | 128K bytes           | E0000-FFFFF <sub>H</sub> |

### **Memory Expansion**

| EPROM with<br>iSBC® 341<br>Board Using: | Capacity   | Address Range            |

|-----------------------------------------|------------|--------------------------|

| 2732                                    | 24K bytes  | F8000-FFFFF <sub>H</sub> |

| 2764                                    | 48K bytes  | F0000-FFFFF <sub>H</sub> |

| 27128                                   | 96K bytes  | E0000-FFFFF <sub>H</sub> |

| 27256                                   | 192K bytes | C0000-FFFFFH             |

### I/O Capacity

Serial—8 programmable lines using four 82530 components

iSBX MULTIMODULE-2 iSBX single-wide boards

### **Serial Communications Characteristics**

Synchronous—Internal or external character synchronization on one or two synchronous characters

Asynchronous—5-8 bits and 1,  $1\frac{1}{2}$ , or 2 stop bits per character; programmable clock factor; break detection and generation; parity, overrun, and framing error detection.

### **Baud Rates**

| S                         | ynchronous<br>X1 Clock         |  |

|---------------------------|--------------------------------|--|

| Baud Rate                 | 82530 Count Value<br>(Decimal) |  |

| 64000                     | 36                             |  |

| 48000                     | 49                             |  |

| 19200                     | 126                            |  |

| 9600                      | 254                            |  |

| 4800                      | 510                            |  |

| 2400                      | 1022                           |  |

| 1800                      | 1363                           |  |

| 1200                      | 2046                           |  |

| 300                       | 8190                           |  |

| Asynchronous<br>X16 Clock |                                |  |

| Baud Rate                 | 82530 Count Value<br>(Decimal) |  |

| 19200                     | 6                              |  |

| 9600                      | 14                             |  |

| 4800                      | 30                             |  |

| 2400                      | 62                             |  |

| 1800                      | 83                             |  |

| 1200                      | 126                            |  |

## Interfaces

300

110

#### **ISBX™ BUS**

The iSBC 188/56 board meets iSBX compliance level D8/8 DMA

510

1394

#### **MULTIBUS® SYSTEM BUS**

The iSBC 188/56 board meets MULTIBUS compliance level Master/Slave D8 M24 I16 VO EL.

#### SERIAL RS232C SIGNALS

| CD      | Carrier             |  |

|---------|---------------------|--|

| CTS     | Clear to Send       |  |

| DSR     | Data Set Ready      |  |

| DTE TXC | Transmit Clock      |  |

| DTR     | Data Terminal Ready |  |

| RTS     | Request to Send     |  |

| RXC     | Receive Clock       |  |

| RXD     | Receive Data        |  |

| SG      | Signal Ground       |  |

| TXD     | Transmit Data       |  |

| RI      | Ring Indicator      |  |

#### RS422A/449 SIGNALS

| RC | Receive Common  |

|----|-----------------|

| RD | Receive Data    |

| RT | Receive Timing  |

| SD | Send Data       |

| TT | Terminal Timing |

# **Environmental Characteristics**

| Temperature: | 0 to 55°0<br>(LFM) Air | C at 200 Linear<br>Velocity | Feet/Min. |

|--------------|------------------------|-----------------------------|-----------|

| Humidity:    | to 90%,<br>70°C)       | non-condensing              | (25°C to  |

# **Physical Characteristics**

Width:

30.48 cm (12.00 in)

Length:

17.15 cm (6.75 in)

Height:

1.04 cm (0.41 in)

Weight:

595 gm (21 oz)

#### **Electrical Characteristics**

The power required per voltage for the iSBC 188/56 board is shown below. These numbers do not include the current required by universal memory sites or expansion modules.

| Voltage<br>(Volts) | Current<br>(Amps) typ. | Power<br>(Watts) typ. |

|--------------------|------------------------|-----------------------|

| +5                 | 4.56A                  | 22.8W                 |

| + 12               | 0.12A                  | 1.5W                  |

| - 12               | 0.11A                  | 1.3W                  |

#### **Reference Manual**

iSBC 188/56 Advanced Data Communications Computer Reference Manual Order Number 148209-001.

## **ORDERING INFORMATION**

Part Number Description

iSBC 188/56 8-Serial Channel Advanced Communicating Computer