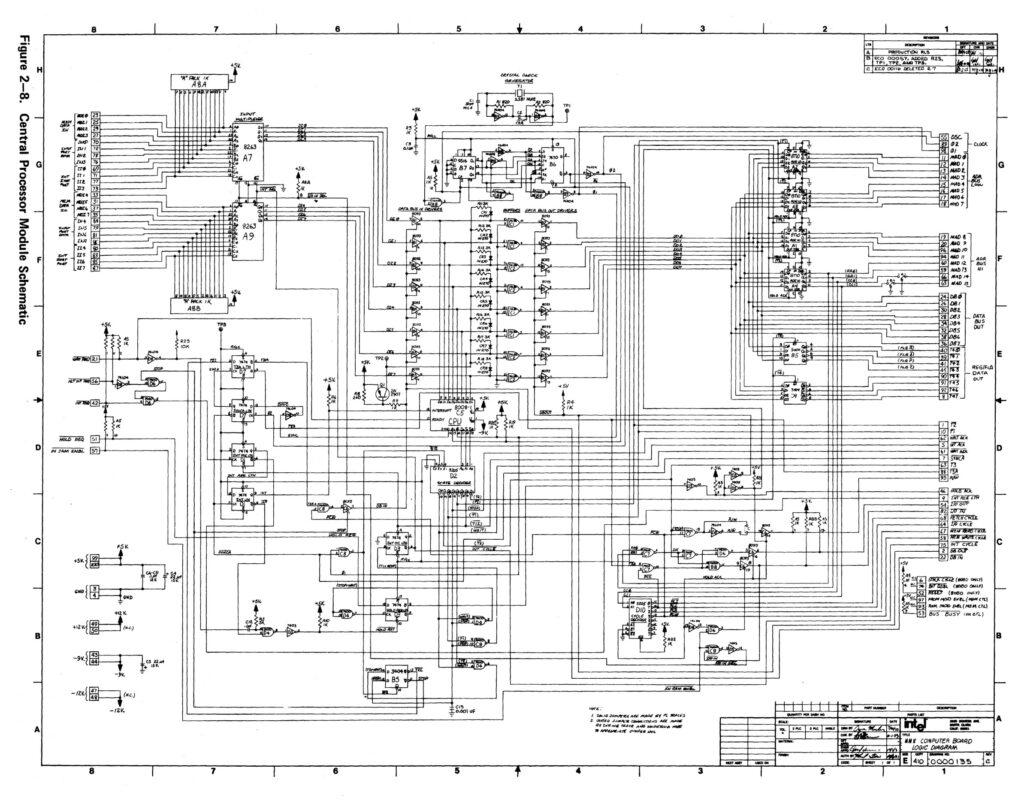

The basic capabilities of the module are obtained through the use of Intel’s 8008-1 monol ith ic CPU. The chip processor provides 48 command instructions, the ability to access over 16K memory bytes directly, 6 working index registers, a seven-level subroutine stack, and interrupt handling capability. The CPU’s instruction set permits I/O and register-to-register transfer, arithmetic and logical operations. Four internal status bits permit conditional jumps based on carry (overflow-underflow), sign, zero, and parity (even). The Central Processor Module contains a crystal controlled clock oscillator which provides a stable timing reference for all circuitry on the board. The use of a selected 8008 (the 8008-1) and an 800 kHz clock permits a basic processor cycle of 12.5 microseconds.

Memcry interface and control logic are included on the module. The imm8-82 contains a latched fourteen-bit address bus, an eight-bit input bus for data from memory, and an eight-bit output bus for data to memory. The module generates signals which identify a memory read, a memory write, or an instruction fetch cycle. These are avai lab Ie for the control of external circuitry. A wait request line permits interfacing the processor module with slow memories.

If minimum access time exceeds one microsecond, the memory controller can request a temporary pause in the processing cycle, causing the processor to wait for the memory’s response to read or a write command.

I/O interface and control are also built into the Central Processor Module. Five digits on the address bus (A9 – A13) are used during I/O operations, to specify one of 32 addressable peripherals. The lower eight addresses (0-7) are reserved for input devices, while the remaining twenty-four (8-31) are used for output. An eight-line data bus for peripheral inputs is included on the module. The output devices share an eight-line output bus with the external memory. Signals generated on the module identify and synchronize I/O operations. These are available for the control of external circuitry.

The imm8-82 is able to process external interrupts. It is equipped with an INTERRUPT request line and with an eight-bit interrupt port. An external device may request service by placing an appropriate instruction code on the interrupt port’s lines and activating the INTERRUPT line.

The Central Processor Module is also equipped with a hold request line, which enables external devices to access memory directly. By issuing a wait request, and following the acknowledged wait with a hold, the memory controller can cause the processor to suspend its operation and relinquish control of the main data bus. This allows an external device to command the bus and to effect memory transfers directly.